Contribution Number: OIF2002.018.00

Working Group: Physical and Link Layer (PLL) Working Group

Title: SFI-4 Phase 2: 64b/66b Line Code Update

Source: Rick Walker

Agilent Labs

rick\_walker@labs.agilent.com

Date: January 28, 2002

Abstract: An update to the proposed 64b/66b line code for SFI-4 Phase 2. Uses a modified form of the 802.3ae 64b/66b code as a physical layer linecode for SFI-4 Phase 2: a protocol independent, 12.5 Gb/s, four wire, chip-to-chip interconnect interface.

Notice: This contribution has been created to assist the Optical Internetwoking Forum (OIF). This document is offered to the OIF solely as a basis for discussion and is not a binding proposal on the companies listed as resources above. Each company in the source list, and the OIF, reserves the rights to at any time to add, amend, or withdraw statements contained herein.

This Working Text represents work in progress by the OIF, and must not be construed as an official OIF Technical Report. Nothing in this document is in way binding on the OIF or any of its members. The document is offered as a basis for discussion and communication, both within and without the OIF.

For additional information contact:

The Optical Internetworking Forum, 39355 California Street, Suite 307, Fremont CA 94538 510-608-5990 phone, info@oiforum.com

SFI-4 Phase 2: 64b/66b Code Update

## SFI-4 Phase 2: 64b/66b Line Code Update

### **Rick Walker**

Agilent Laboratories, Palo Alto, CA rick\_walker@labs.agilent.com

### Richard Dugan, Allan Liu

Agilent Technologies, Semiconductor Products Group, San Jose, CA richard\_dugan@agilent.com, allan\_liu@agilent.com

# Topics

- Motivation

- Code Review

- Coder/Decoder Block Diagrams

- Comparison with 8B/10B

- Eye diagram margins

- Spectrum with static data

- Capacitive coupling

- Summary

# Motivation and Strategy

- Allow protocol-agnostic "virtual ribbon-cable" operation

- Leverage existing 64b/66b code to reduce design time and risk

- Reduce pin count, routing complexity, and power dissipation

- Eliminate deskew channel to reduce number of highspeed lines by 25%

- Minimize coding overhead to permit strong FEC

# Code Overview

Use a simplified version of 64b/66b 10GbE linecode

- Data is transmitted in 8 byte (64-bit) blocks

- Each block is scrambled at the transmitter and descrambled at the receiver to ensure statistical DCbalance and transition density for RX PLL

- Block/byte alignment is provided by prepending each scrambled 64 bit block with two non-scrambled "01" sync bits, creating an overall 66 bit frame

- 802.3ae allows for non-data (control) frames indicated by a "10" sync pattern, but these codes are not needed, nor are proposed for SFI-4

# Comparison with SONET

- two-bit preamble is analogous to SONET's A1/A2 sync bytes.

- SONET CDRs are designed to accommodate an 80 bit run length. This new code is deterministically limited to 64 bit run length due to the periodic preamble bits.

- Both codes use similar bit-slipping method to acquire frame sync.

- This code is similar in spirit to the SONET code. It is not in any way compatible, but inherits much of SONET properties while being much simpler to implement.

- Much less on-chip buffering required

- Lower latency

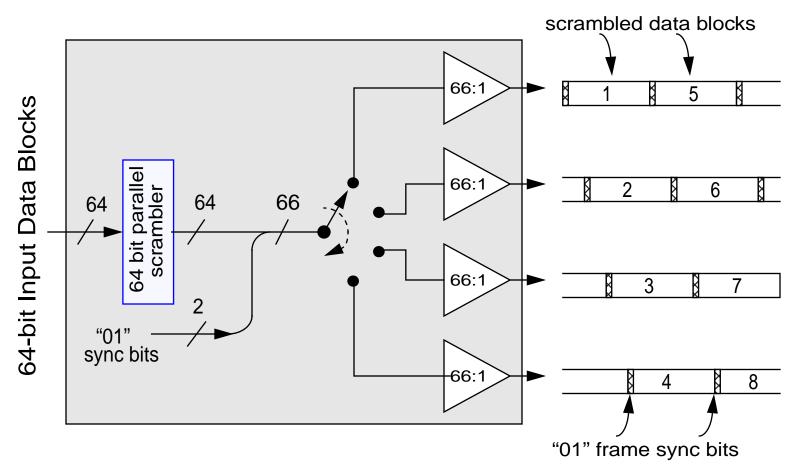

## Coder Block Diagram

Coder is a simplified 64b/66b codec (data frames only), with 66 bit frames sent round-robin across the 4 output lanes.

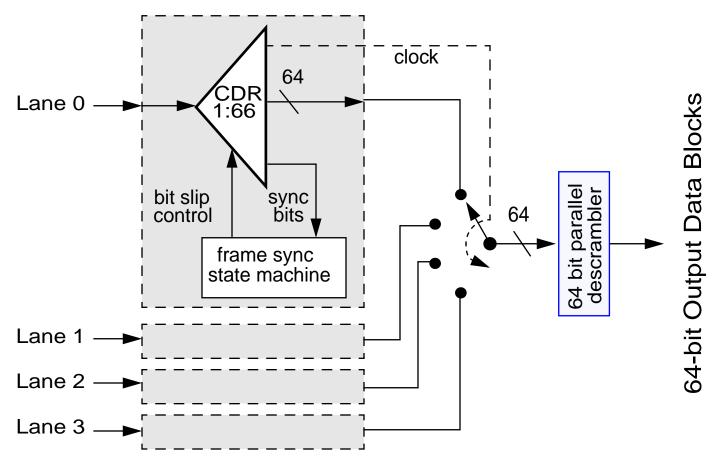

### Decoder Block Diagram

Deskew logic uses recovered Lane 0 clock phases to optimally sample other lanes with +/- 16 bits of skew tolerance

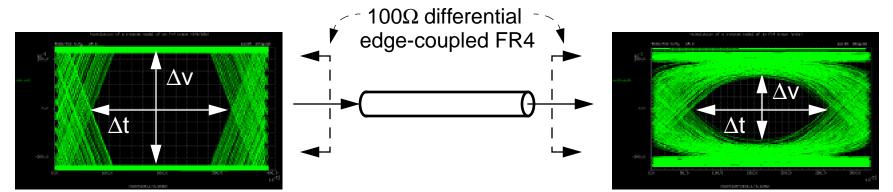

# Eye Diagram Simulation Setup

ADS stripline model parameters:

trace spacing =10 mil, width = 5 mil, thickness = 1.17 mil, tan $\delta$  = 0.03,

$Z_0 = 50\Omega$ ,  $\varepsilon_r = 4.5$ , dielectric thickness = 16mil.

#### Transmitted data patterns:

TJ=0.35UI, 463 mV pk/pk, tr/tf=83ps (worst-case SXI-5 transmit eye pattern)

- 8B/10B: x7+x6+1 pattern at 3.125 Gb/s.

- 64b/66b: 0,1 followed by 64 random bits from  $2^{32}$ -1 pattern at 2.58Gb/s.

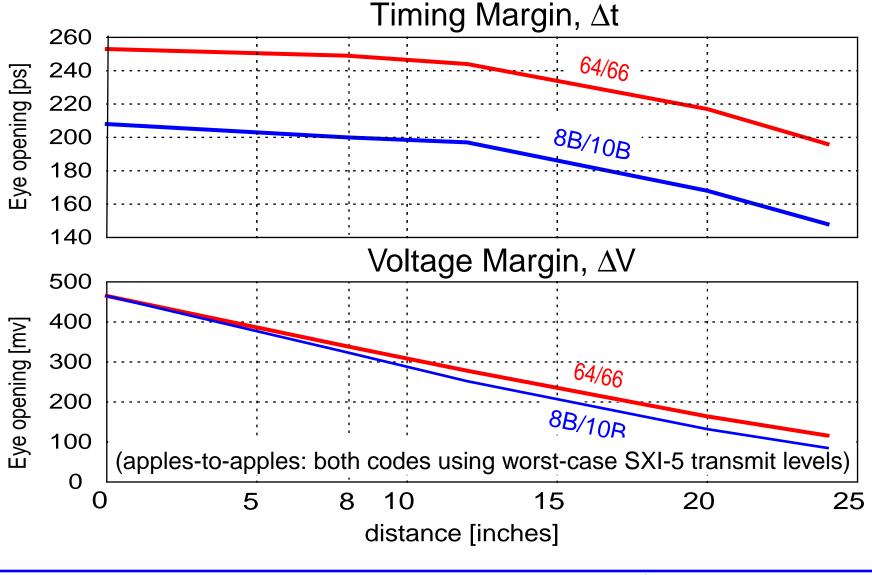

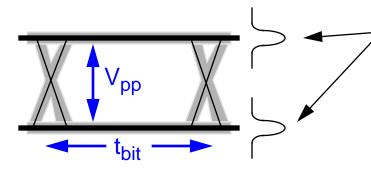

# 8b/10b, 64b/66b Simulated Eye Margins

Optical Internetworking Forum San Diego, CA Jan. 28-30, 2002 SFI-4 Phase 2: 64b/66b Code Update

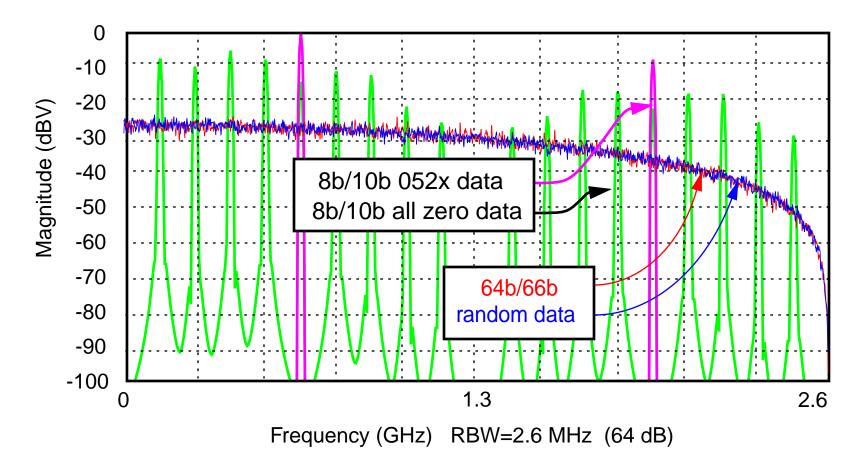

# **Spectral Properties**

8b/10b spectrum is not well behaved with static input data patterns. 64b/66b is data agnostic.

## **Baseline Wander**

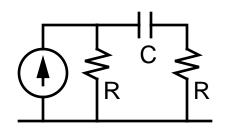

A typical laser system will require a coupling capacitor at both TX and RX time constant (tau) = 2\*R\*C

Eye diagram shows Gaussian wander (with stddev of sigma) due to statistical of 1's and 0's in charging coupling capacitor C.

The average value of N random bits is 1/2 with a sigma of 1/sqrt(N)A coupling capacitor can be approximately considered to be performing a moving average over N bits, where N ~= 8\*tau/(tbit)

$$\sigma(offset) = V_{pp} \sqrt{\frac{t_{bit}}{8\tau}}$$

Optical Internetworking Forum San Diego, CA Jan. 28-30, 2002

SFI-4 Phase 2: 64b/66b Code Update

## coupling capacitor analysis

$$\sigma(offset) = V_{pp} \sqrt{\frac{t_{bit}}{8\tau}}$$

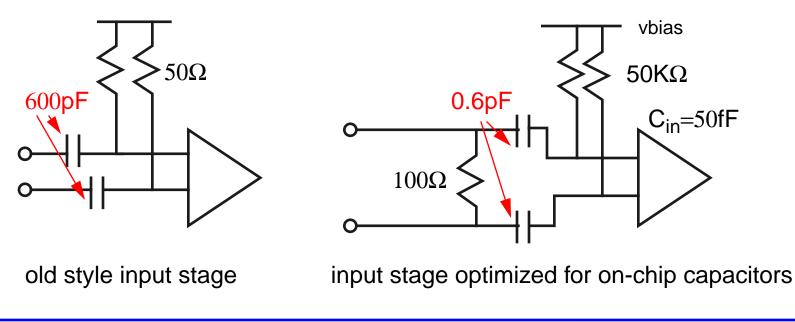

tbit = 388pS, Vpp=500mV, if we desire <100mV total baseline wander at  $10^{-12}$  BER, then  $\sigma$ =20mV, therefore  $\tau$  = 30nS. At 50 $\Omega$  impedance we need 600pF, at 50K $\Omega$  impedance, we only require 0.6pF!

Optical Internetworking Forum San Diego, CA Jan. 28-30, 2002

SFI-4 Phase 2: 64b/66b Code Update

# Summary

- Eliminates deskew lanes

- Fits within 70 pin connector

- Ensures DC balance on all lanes

- Limits run-length to a maximum of 66 bits

- Single 64b/66b codec required

- Simple deskew accomodates 16 bits of skew

- 3.125% coding overhead

- Protocol Agnostic (virtual ribbon cable)

- Leverages existing 802.3ae 64b/66b code